1. see here. Increasing the file descriptor limit

2. see APUE, getrlimit, setrlimit()

Wednesday, December 19, 2007

Tuesday, December 11, 2007

when to recv() returns?

Basically, there are three conditions:

* The receive buffer is full. Here, the receive buffer means either

the buffer we submit or the intermediate winsock buffer.

* 500ms has passed since the last arrival of data.

* Data arrives with the PUSH-bit set.

the original post is here.

* The receive buffer is full. Here, the receive buffer means either

the buffer we submit or the intermediate winsock buffer.

* 500ms has passed since the last arrival of data.

* Data arrives with the PUSH-bit set.

the original post is here.

Sunday, November 11, 2007

Saturday, October 13, 2007

x86_64, IA-64两种64位CPU

x86_64和IA-64是两种64位CPU,其中x86_64是由AMD于2000年提出

并于2003年制造出第一款芯片,其主要特点它的Long Mode保持对80386

体系结构的向下兼容。后来AMD称之为AMD64。Intel最初在2004年的IDF

上宣称支持这种类型的芯片,刚开始被成为CT, IA-32e, EM64T, 2006年

命名为Intel64.

AMD64和Intel64在指令集上大同小异,Linux操作系统的x86_64可以支持

两种CPU。在x86_64的开发上,AMD占领了先机。但事实上Intel早在1997

年就开始设计x86_64 CPU,迟迟未向外界公布的原因在于Intel在此期间

在推它的IA-64 CPU。后来面临AMD的市场压力,才在2004 IDF上公布有关

x86_64的开发进展。

IA-64是HP最早于1989年提出一种基于RISC的EPIC技术,并最终替代高端

的所有基于RISC和CISC技术的芯片。HP与Intel与1994年结盟,联合开放

IA-64,预期1998年生产出来。但由于技术的复杂性,1999年10月, Intel

才推出Itanium I代。2002年推出II代。IA-64主要针对HPC和Enterprise

Server的应用。与Sun UltraSPARC T2, IBM Power6, Fujitsu's

SPARC64,以及x86_64竞争。

IA-64的优势主要集中在浮点运算,主要在科学计算上使用。Web Server

不太会用到IA-64的这个强项。因此,市场前景尚不明朗。

参考页面:

[1] http://en.wikipedia.org/wiki/X86-64

[2] http://en.wikipedia.org/wiki/IA-64

并于2003年制造出第一款芯片,其主要特点它的Long Mode保持对80386

体系结构的向下兼容。后来AMD称之为AMD64。Intel最初在2004年的IDF

上宣称支持这种类型的芯片,刚开始被成为CT, IA-32e, EM64T, 2006年

命名为Intel64.

AMD64和Intel64在指令集上大同小异,Linux操作系统的x86_64可以支持

两种CPU。在x86_64的开发上,AMD占领了先机。但事实上Intel早在1997

年就开始设计x86_64 CPU,迟迟未向外界公布的原因在于Intel在此期间

在推它的IA-64 CPU。后来面临AMD的市场压力,才在2004 IDF上公布有关

x86_64的开发进展。

IA-64是HP最早于1989年提出一种基于RISC的EPIC技术,并最终替代高端

的所有基于RISC和CISC技术的芯片。HP与Intel与1994年结盟,联合开放

IA-64,预期1998年生产出来。但由于技术的复杂性,1999年10月, Intel

才推出Itanium I代。2002年推出II代。IA-64主要针对HPC和Enterprise

Server的应用。与Sun UltraSPARC T2, IBM Power6, Fujitsu's

SPARC64,以及x86_64竞争。

IA-64的优势主要集中在浮点运算,主要在科学计算上使用。Web Server

不太会用到IA-64的这个强项。因此,市场前景尚不明朗。

参考页面:

[1] http://en.wikipedia.org/wiki/X86-64

[2] http://en.wikipedia.org/wiki/IA-64

Friday, September 28, 2007

linux PACKET_MMAP

从2.4起,Linux支持MMAP的数据包采集,检查内核选项

CONFIG_PACKET_MMAP=y

同时需要使用支持PACKET_RING的libpcap版本,这里。

下载后编译时使用如下命令

./configure --enable-shared=yes

将生成的动态连接库libpcap.so等拷贝到/usr/lib下就可以

使用了。因为使用动态连接库,因此应用程序无须重新编译。

运行时需要设置环境变量PCAP_FRAMES=30000,这样

open_pcap_live()才会使用PACKET_RING, 如果没有这个

变量则使用普通的AF_PACKET抓包。

性能:

千兆下抓包,大概100Mbps的TCP文件传输,现在使用PACKET_RING不丢包,

CPU占用率20%左右。之前要丢10%的包,

CONFIG_PACKET_MMAP=y

同时需要使用支持PACKET_RING的libpcap版本,这里。

下载后编译时使用如下命令

./configure --enable-shared=yes

将生成的动态连接库libpcap.so等拷贝到/usr/lib下就可以

使用了。因为使用动态连接库,因此应用程序无须重新编译。

运行时需要设置环境变量PCAP_FRAMES=30000,这样

open_pcap_live()才会使用PACKET_RING, 如果没有这个

变量则使用普通的AF_PACKET抓包。

性能:

千兆下抓包,大概100Mbps的TCP文件传输,现在使用PACKET_RING不丢包,

CPU占用率20%左右。之前要丢10%的包,

Wednesday, August 29, 2007

NUMA, smp and AMD Intel

一直对NUMA体系结构没有直观的认识,看了FAQ: NUMA, SMP and AMDs Direct Connect Architecture才知道AMD Opteron双核采用的是NUMA结构。与SMP结构不同,主存不是通过Memory controller连接到CPUs,NUMA中不同的内存条直接连接到不同的CPU上。这样的好处在于可扩展性高,CPU可以独立访问属于自己的CPU,Memory controller不会成为系统的瓶颈。但缺点在于访问其它片的内存条用时会增加。这需要操作系统和进程进行优化才能发挥NUMA体系结构的好处。

目前Linux已经很好的支持SMP,有关NUMA的支持还不够完善。SUSE Linux Enterprise Server 9 队NUMA有较好的支持。

目前Linux已经很好的支持SMP,有关NUMA的支持还不够完善。SUSE Linux Enterprise Server 9 队NUMA有较好的支持。

Monday, August 27, 2007

dynamips for CCIEs

Started in August of 2005 by Christophe Fillot, Dynamips is a Linux and Windows based application that is used to emulate the hardware of the Cisco 7200 and 3600 series routing platforms. Unlike traditional router “simulators" Dynamips allows you to boot real Cisco IOS software images and build complex network topologies to test the functionality of IOS on your desktop PC. As of November 2006 Dynamips currently supports Ethernet, Serial, ATM, and POS interfaces for the 7200 series routers and Ethernet, Serial, and Etherswitch modules for the 3600 series routers. Best of all Dynamips is open-source and free to download!

Monday, March 19, 2007

魔鬼星期一

* 10:00, 到实验室处理本科生的毕业设计,一起制定这个星期的计划。

* 然后是个硕士生,问了问进展。

* 接着收到中心来信,同意买网卡,于是赶紧联系。一问,

型号不符,解释了一大圈总于明白是厂家直销和OEM的区别。

搞定,放下...

* 接着收到教授来信,说paper缺少理论,要争取加个理论补实验。

还剩一个月的时间,硬着头皮也要上啊。

* 收到中心来信,说27号Intel网卡技术问答会,要我参加。ok.

* 接着教授msg我打听一个申请学生的情况,我也不认识。怎么办?

找朋友打听。

* 中午吃饭,和师弟聊了有关项目的进展。决定这周开个小组讨论会,

让参加者报告计划。下午回来联系,定于周三下午4:00.

* 14:00, 打听情况,搞定。

* 看论文

* 15:00, 马杯报名需学生证首页复印件,交。

* 看论文,寻找理论灵感。未果。

* 晚饭回来,看师弟的论文,23号globecom截稿。

* 7:00,实验室项目周三交中期调研报告,让我参加头脑风暴。

大家乱抓一气,居然成功了!

* 9:30-10:30, 和师弟讨论文章,结构大改。改完再发来看。

* 然后是个硕士生,问了问进展。

* 接着收到中心来信,同意买网卡,于是赶紧联系。一问,

型号不符,解释了一大圈总于明白是厂家直销和OEM的区别。

搞定,放下...

* 接着收到教授来信,说paper缺少理论,要争取加个理论补实验。

还剩一个月的时间,硬着头皮也要上啊。

* 收到中心来信,说27号Intel网卡技术问答会,要我参加。ok.

* 接着教授msg我打听一个申请学生的情况,我也不认识。怎么办?

找朋友打听。

* 中午吃饭,和师弟聊了有关项目的进展。决定这周开个小组讨论会,

让参加者报告计划。下午回来联系,定于周三下午4:00.

* 14:00, 打听情况,搞定。

* 看论文

* 15:00, 马杯报名需学生证首页复印件,交。

* 看论文,寻找理论灵感。未果。

* 晚饭回来,看师弟的论文,23号globecom截稿。

* 7:00,实验室项目周三交中期调研报告,让我参加头脑风暴。

大家乱抓一气,居然成功了!

* 9:30-10:30, 和师弟讨论文章,结构大改。改完再发来看。

Monday, October 30, 2006

IXP的硬件线程和Xeon的超线程

根据Intel的网络处理器IXP2004的产品资料,其核心处理单元

微引擎uEngine针对网络数据包处理做了专门的优化。其中最

重要的优化就是硬件线程,“每个uEngine可以管理8个硬件线程,

并可达到线程间的切换零延迟”。

硬件线程是一种SMT(Simultaneous Multithreading Technology)

技术。通过在一个CPU上维护多套指令状态保存器,使得几个线程

可以共用该CPU的运算单元。当一个线程I/O阻塞时,其它线程可以

快速被切换。这种技术和Xeon系列的HyperThreading技术实质

是一样的。

超线程技术对于程序执行效率的提高主要来源于当其中一个

线程出现I/O瓶颈时(比如cache miss, branch misprediction,

或者data dependency时),另一个线程可以迅速切入。只有当

这种效应比较严重时,超线程才能提高大幅度系统性能,因为即使

硬件线程切换也会有开销的。

一般来说,对于包的实时处理中,这种瓶颈应该不会特别多,

因此硬件线程可能并不能很有效提高包处理的性能。

参考资料:

http://en.wikipedia.org/wiki/Hyperthreading

http://www.theregister.co.uk/2002/06/18/what_the_hell_is_hyperthreading/

微引擎uEngine针对网络数据包处理做了专门的优化。其中最

重要的优化就是硬件线程,“每个uEngine可以管理8个硬件线程,

并可达到线程间的切换零延迟”。

硬件线程是一种SMT(Simultaneous Multithreading Technology)

技术。通过在一个CPU上维护多套指令状态保存器,使得几个线程

可以共用该CPU的运算单元。当一个线程I/O阻塞时,其它线程可以

快速被切换。这种技术和Xeon系列的HyperThreading技术实质

是一样的。

超线程技术对于程序执行效率的提高主要来源于当其中一个

线程出现I/O瓶颈时(比如cache miss, branch misprediction,

或者data dependency时),另一个线程可以迅速切入。只有当

这种效应比较严重时,超线程才能提高大幅度系统性能,因为即使

硬件线程切换也会有开销的。

一般来说,对于包的实时处理中,这种瓶颈应该不会特别多,

因此硬件线程可能并不能很有效提高包处理的性能。

参考资料:

http://en.wikipedia.org/wiki/Hyperthreading

http://www.theregister.co.uk/2002/06/18/what_the_hell_is_hyperthreading/

Saturday, October 14, 2006

使用pdb调试python

前些日子在blogden的帖子介绍了一种调试方法,在程序中产生异常,这相当于c语言中加入assert()语句。"Automatic invocation of pdb on exceptions"

另一种方法则是在程序中插入断点,在你需要插入断点地方插入语句:

另一种方法则是在程序中插入断点,在你需要插入断点地方插入语句:

import pdb; pdb.set_trace()参考http://plone.org/documentation/how-to/using-pdb

Wednesday, October 11, 2006

15454的配置

最近拿到一台新的cisco 15454交换机,上次15454的初始配置是cisco技术人员完成的。这次,他们发过来一台裸机,所有的配置都需要我们自己完成。

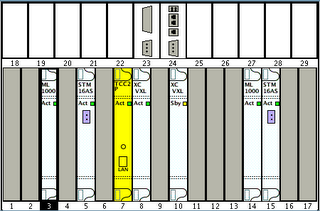

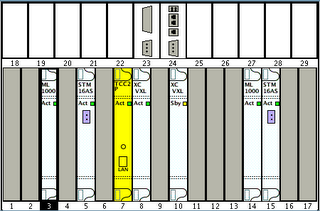

版卡配置情况

1. 1块TCC2

2. 2块XCVXL(10G)

3. 2块ML1000-2

4. 2快STM16

5. 电源模块

另外还有电源线

第一步:接电源线

15454使用外部48V 3A直流电源输入,首先让电工将电源线作好,接入15454顶部的电源模块。15454使用双电源供电,第二块电源做为备份。由于我们只是进行实验,因此只接了单电源。这导致在CTC控制面板中一直会出线备份电源失效的警告。

第二步:接网线

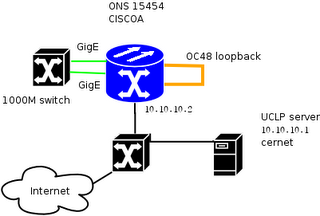

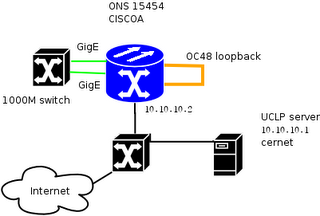

网线连接如图,

1. TCC的控制网口连接到一台交换机上

1. TCC的控制网口连接到一台交换机上

2. 每块ML1000卡的一个GE0端口接到一台交换机上

3. 两块STM16卡的STM16端口对接起来

网线连接完毕后发现ML1000卡的GE口工作指示灯并不亮,肉眼看了一下该口的TX端口,发现没有亮光。这可能是由于该口尚未配置的缘故。因此,需要登陆CTC对ML1000卡进行配置。

第三步:登陆CTC

通过15454下面的控制面板看到TCC控制端口的IP是10.10.10.2,在浏览器中访问http://10.10.10.2可以登陆CTC。成功登陆后发现这台15454的CTC版本是7.00,比上次5.0的版本高一些。但是,在CTC中选择open IOS connection并不成功,查阅15454 troubleshooting资料发现这是由于ML1000缺少初始化配置文件造成的。

第三步:配置ML1000卡

15454 Ethercard Guide第3章"Start Configuration File"中提到,在ML1000缺少初始化配置文件时,无法从CTC登陆。此时需要通过Serial Console Port或者选择从CTC载入IOS Startup配置文件。由于手头没有Startup配置文件的样本,因此选择第一种方式。找到一个console线,在服务器上运行gtkterm,根据该节"Configuring the Management Port"的步骤配置好一个ML1000卡。将该配置文件通过CTC下载本机,再使用第二种配置方式将另一个ML1000卡配置好了。

第四步:系统时钟的调整

检查CTC当前的警告信息,发现(LOS)BITS-{1,2}, (SYNCPRI)SYNC-NE的警告信息。查阅troubleshooting手册,发现这些警告是由于给15454配置了不正确的外部时钟源造成的。15454总的来说是一台SDH设备,因此会使用外部使用来进行精确的时间同步。然而在我们的实验中并没有接入外部时钟源,因此需要内部时钟源。参考procedure guide中步骤DLP-D70为15454配置内部时钟源,成功消除这些警告。

最后再看一下警告面板,只有一个PWR-B失效的警告,这是由于我们没有使用备份电源造成的。OK. 至此一台15454裸机成功配置成功。下面我们将在这台机器上开展uclp2.0的实验,zk将为你带来。

版卡配置情况

1. 1块TCC2

2. 2块XCVXL(10G)

3. 2块ML1000-2

4. 2快STM16

5. 电源模块

另外还有电源线

第一步:接电源线

15454使用外部48V 3A直流电源输入,首先让电工将电源线作好,接入15454顶部的电源模块。15454使用双电源供电,第二块电源做为备份。由于我们只是进行实验,因此只接了单电源。这导致在CTC控制面板中一直会出线备份电源失效的警告。

第二步:接网线

网线连接如图,

1. TCC的控制网口连接到一台交换机上

1. TCC的控制网口连接到一台交换机上2. 每块ML1000卡的一个GE0端口接到一台交换机上

3. 两块STM16卡的STM16端口对接起来

网线连接完毕后发现ML1000卡的GE口工作指示灯并不亮,肉眼看了一下该口的TX端口,发现没有亮光。这可能是由于该口尚未配置的缘故。因此,需要登陆CTC对ML1000卡进行配置。

第三步:登陆CTC

通过15454下面的控制面板看到TCC控制端口的IP是10.10.10.2,在浏览器中访问http://10.10.10.2可以登陆CTC。成功登陆后发现这台15454的CTC版本是7.00,比上次5.0的版本高一些。但是,在CTC中选择open IOS connection并不成功,查阅15454 troubleshooting资料发现这是由于ML1000缺少初始化配置文件造成的。

第三步:配置ML1000卡

15454 Ethercard Guide第3章"Start Configuration File"中提到,在ML1000缺少初始化配置文件时,无法从CTC登陆。此时需要通过Serial Console Port或者选择从CTC载入IOS Startup配置文件。由于手头没有Startup配置文件的样本,因此选择第一种方式。找到一个console线,在服务器上运行gtkterm,根据该节"Configuring the Management Port"的步骤配置好一个ML1000卡。将该配置文件通过CTC下载本机,再使用第二种配置方式将另一个ML1000卡配置好了。

第四步:系统时钟的调整

检查CTC当前的警告信息,发现(LOS)BITS-{1,2}, (SYNCPRI)SYNC-NE的警告信息。查阅troubleshooting手册,发现这些警告是由于给15454配置了不正确的外部时钟源造成的。15454总的来说是一台SDH设备,因此会使用外部使用来进行精确的时间同步。然而在我们的实验中并没有接入外部时钟源,因此需要内部时钟源。参考procedure guide中步骤DLP-D70为15454配置内部时钟源,成功消除这些警告。

最后再看一下警告面板,只有一个PWR-B失效的警告,这是由于我们没有使用备份电源造成的。OK. 至此一台15454裸机成功配置成功。下面我们将在这台机器上开展uclp2.0的实验,zk将为你带来。

Saturday, October 07, 2006

CPU的一些常识

MIPS: Millon Instructions per second, 每秒钟指令执行速度。

时钟频率:

早期的电脑,大约每个指令需要15个时钟周期,而现在只需要1~2个时钟周期。

这是因为,现在CPU使用pipeline的技术。虽然每条指令仍需要多个时钟周期来完成,

“In a pipelined architecture, instruction execution overlaps. So even though it might take five clock cycles to execute each instruction, there can be five instructions in various stages of execution simultaneously. That way it looks like one instruction completes every clock cycle.”

64-bit CPU的好处:

1. 内存地址空间扩大,32位CPU内存大小限制2GB

2. 64-bit微机能够提供更快的I/O速度

对于普通用户,64微机带来的好处并不多。

参考:

http://computer.howstuffworks.com/microprocessor.htm

时钟频率:

早期的电脑,大约每个指令需要15个时钟周期,而现在只需要1~2个时钟周期。

这是因为,现在CPU使用pipeline的技术。虽然每条指令仍需要多个时钟周期来完成,

“In a pipelined architecture, instruction execution overlaps. So even though it might take five clock cycles to execute each instruction, there can be five instructions in various stages of execution simultaneously. That way it looks like one instruction completes every clock cycle.”

64-bit CPU的好处:

1. 内存地址空间扩大,32位CPU内存大小限制2GB

2. 64-bit微机能够提供更快的I/O速度

对于普通用户,64微机带来的好处并不多。

参考:

http://computer.howstuffworks.com/microprocessor.htm

Friday, September 22, 2006

主板的一些工作原理

现代主板的工作原理:

1. 北桥芯片(northbridge)通过FSB连接CPU, 内存, AGP显卡和南桥芯片(southbridge)。南桥芯片连接计算机的其它外设,比如ATA硬盘(PATA或者SATA), PCI扩展口,USB接口等等。

2. 各种连接总线(Various Buses)

a. Front Side Bus: 连接北桥芯片和CPU, 1066/800/533MHz

b. Back Side Bus: 连接CPU芯片和主板上的2级缓存

b. Memory Bus: 连接北桥芯片和内存条,133/266/400/533MHz

c. AGP Bus: 连接北桥芯片和AGP显卡,通常是66MHz

d. PCI Bus: 连接南桥芯片和PCI, 33MHz

3. 内存

a. SDRAM

b. DDR(Dual Data Rate) SDRAM内存:取决于Memory Bus的频率,传输

速率为 xMHz * 64bit / 8 = 8xBytes/seconds. DDR400的传输速率能够达到

3200MBytes/sec。

c. DDR Dual Channel: 能够将内存传输速率增长一倍

4. PCI

a. 最初PCI是33MHz, 32bits, 传输速率为132MBytes/sec

b. 后来出现PCI 64bits/33MHz, 64bits/66MHz, 目前PCI-X工作

在64bits/133MHz, 传输速率为1GBytes/sec.

c. PCI-X是Intel早先推出针对服务器市场的,现在的PCI-Express

是针对普通PC市场。

d. PCI支持PnP。支持PnP需要PnP Bios, PCI的ESCD和操作系统的

支持。其中PCI设备上的ESCD包含了该PCI卡的各种信息

e. 目前PCI还是共享总线型的传输方式,即PCI总线上同一时刻只允许

一个PCI设备进行数据传输(参考资料)。(AMD提出的Hyper-Transport技术则

用于在任意两个设备之间建立点到点的数据传输线路,解决总线方式的

不足)

参考资料:

1. How motherboard works, http://computer.howstuffworks.com/motherboard.htm

2. How RAM works, http://computer.howstuffworks.com/ram.htm

3. How PCI works, http://computer.howstuffworks.com/pci.htm

4. PCI-Express, http://arstechnica.com/articles/paedia/hardware/pcie.ars/1

1. 北桥芯片(northbridge)通过FSB连接CPU, 内存, AGP显卡和南桥芯片(southbridge)。南桥芯片连接计算机的其它外设,比如ATA硬盘(PATA或者SATA), PCI扩展口,USB接口等等。

2. 各种连接总线(Various Buses)

a. Front Side Bus: 连接北桥芯片和CPU, 1066/800/533MHz

b. Back Side Bus: 连接CPU芯片和主板上的2级缓存

b. Memory Bus: 连接北桥芯片和内存条,133/266/400/533MHz

c. AGP Bus: 连接北桥芯片和AGP显卡,通常是66MHz

d. PCI Bus: 连接南桥芯片和PCI, 33MHz

3. 内存

a. SDRAM

b. DDR(Dual Data Rate) SDRAM内存:取决于Memory Bus的频率,传输

速率为 xMHz * 64bit / 8 = 8xBytes/seconds. DDR400的传输速率能够达到

3200MBytes/sec。

c. DDR Dual Channel: 能够将内存传输速率增长一倍

4. PCI

a. 最初PCI是33MHz, 32bits, 传输速率为132MBytes/sec

b. 后来出现PCI 64bits/33MHz, 64bits/66MHz, 目前PCI-X工作

在64bits/133MHz, 传输速率为1GBytes/sec.

c. PCI-X是Intel早先推出针对服务器市场的,现在的PCI-Express

是针对普通PC市场。

d. PCI支持PnP。支持PnP需要PnP Bios, PCI的ESCD和操作系统的

支持。其中PCI设备上的ESCD包含了该PCI卡的各种信息

e. 目前PCI还是共享总线型的传输方式,即PCI总线上同一时刻只允许

一个PCI设备进行数据传输(参考资料)。(AMD提出的Hyper-Transport技术则

用于在任意两个设备之间建立点到点的数据传输线路,解决总线方式的

不足)

参考资料:

1. How motherboard works, http://computer.howstuffworks.com/motherboard.htm

2. How RAM works, http://computer.howstuffworks.com/ram.htm

3. How PCI works, http://computer.howstuffworks.com/pci.htm

4. PCI-Express, http://arstechnica.com/articles/paedia/hardware/pcie.ars/1

Subscribe to:

Posts (Atom)