根据Intel的网络处理器IXP2004的产品资料,其核心处理单元

微引擎uEngine针对网络数据包处理做了专门的优化。其中最

重要的优化就是硬件线程,“每个uEngine可以管理8个硬件线程,

并可达到线程间的切换零延迟”。

硬件线程是一种SMT(Simultaneous Multithreading Technology)

技术。通过在一个CPU上维护多套指令状态保存器,使得几个线程

可以共用该CPU的运算单元。当一个线程I/O阻塞时,其它线程可以

快速被切换。这种技术和Xeon系列的HyperThreading技术实质

是一样的。

超线程技术对于程序执行效率的提高主要来源于当其中一个

线程出现I/O瓶颈时(比如cache miss, branch misprediction,

或者data dependency时),另一个线程可以迅速切入。只有当

这种效应比较严重时,超线程才能提高大幅度系统性能,因为即使

硬件线程切换也会有开销的。

一般来说,对于包的实时处理中,这种瓶颈应该不会特别多,

因此硬件线程可能并不能很有效提高包处理的性能。

参考资料:

http://en.wikipedia.org/wiki/Hyperthreading

http://www.theregister.co.uk/2002/06/18/what_the_hell_is_hyperthreading/

Monday, October 30, 2006

Saturday, October 14, 2006

使用pdb调试python

前些日子在blogden的帖子介绍了一种调试方法,在程序中产生异常,这相当于c语言中加入assert()语句。"Automatic invocation of pdb on exceptions"

另一种方法则是在程序中插入断点,在你需要插入断点地方插入语句:

另一种方法则是在程序中插入断点,在你需要插入断点地方插入语句:

import pdb; pdb.set_trace()参考http://plone.org/documentation/how-to/using-pdb

Wednesday, October 11, 2006

15454的配置

最近拿到一台新的cisco 15454交换机,上次15454的初始配置是cisco技术人员完成的。这次,他们发过来一台裸机,所有的配置都需要我们自己完成。

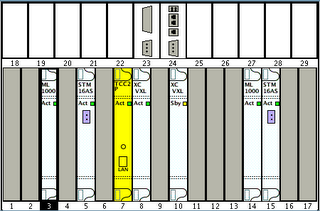

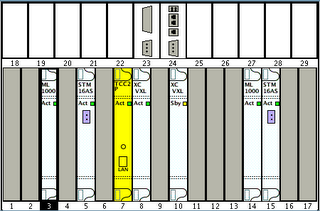

版卡配置情况

1. 1块TCC2

2. 2块XCVXL(10G)

3. 2块ML1000-2

4. 2快STM16

5. 电源模块

另外还有电源线

第一步:接电源线

15454使用外部48V 3A直流电源输入,首先让电工将电源线作好,接入15454顶部的电源模块。15454使用双电源供电,第二块电源做为备份。由于我们只是进行实验,因此只接了单电源。这导致在CTC控制面板中一直会出线备份电源失效的警告。

第二步:接网线

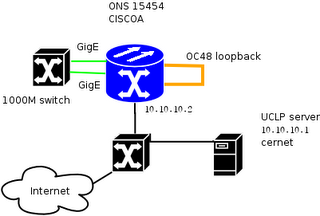

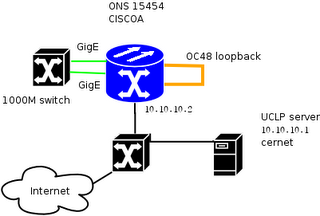

网线连接如图,

1. TCC的控制网口连接到一台交换机上

1. TCC的控制网口连接到一台交换机上

2. 每块ML1000卡的一个GE0端口接到一台交换机上

3. 两块STM16卡的STM16端口对接起来

网线连接完毕后发现ML1000卡的GE口工作指示灯并不亮,肉眼看了一下该口的TX端口,发现没有亮光。这可能是由于该口尚未配置的缘故。因此,需要登陆CTC对ML1000卡进行配置。

第三步:登陆CTC

通过15454下面的控制面板看到TCC控制端口的IP是10.10.10.2,在浏览器中访问http://10.10.10.2可以登陆CTC。成功登陆后发现这台15454的CTC版本是7.00,比上次5.0的版本高一些。但是,在CTC中选择open IOS connection并不成功,查阅15454 troubleshooting资料发现这是由于ML1000缺少初始化配置文件造成的。

第三步:配置ML1000卡

15454 Ethercard Guide第3章"Start Configuration File"中提到,在ML1000缺少初始化配置文件时,无法从CTC登陆。此时需要通过Serial Console Port或者选择从CTC载入IOS Startup配置文件。由于手头没有Startup配置文件的样本,因此选择第一种方式。找到一个console线,在服务器上运行gtkterm,根据该节"Configuring the Management Port"的步骤配置好一个ML1000卡。将该配置文件通过CTC下载本机,再使用第二种配置方式将另一个ML1000卡配置好了。

第四步:系统时钟的调整

检查CTC当前的警告信息,发现(LOS)BITS-{1,2}, (SYNCPRI)SYNC-NE的警告信息。查阅troubleshooting手册,发现这些警告是由于给15454配置了不正确的外部时钟源造成的。15454总的来说是一台SDH设备,因此会使用外部使用来进行精确的时间同步。然而在我们的实验中并没有接入外部时钟源,因此需要内部时钟源。参考procedure guide中步骤DLP-D70为15454配置内部时钟源,成功消除这些警告。

最后再看一下警告面板,只有一个PWR-B失效的警告,这是由于我们没有使用备份电源造成的。OK. 至此一台15454裸机成功配置成功。下面我们将在这台机器上开展uclp2.0的实验,zk将为你带来。

版卡配置情况

1. 1块TCC2

2. 2块XCVXL(10G)

3. 2块ML1000-2

4. 2快STM16

5. 电源模块

另外还有电源线

第一步:接电源线

15454使用外部48V 3A直流电源输入,首先让电工将电源线作好,接入15454顶部的电源模块。15454使用双电源供电,第二块电源做为备份。由于我们只是进行实验,因此只接了单电源。这导致在CTC控制面板中一直会出线备份电源失效的警告。

第二步:接网线

网线连接如图,

1. TCC的控制网口连接到一台交换机上

1. TCC的控制网口连接到一台交换机上2. 每块ML1000卡的一个GE0端口接到一台交换机上

3. 两块STM16卡的STM16端口对接起来

网线连接完毕后发现ML1000卡的GE口工作指示灯并不亮,肉眼看了一下该口的TX端口,发现没有亮光。这可能是由于该口尚未配置的缘故。因此,需要登陆CTC对ML1000卡进行配置。

第三步:登陆CTC

通过15454下面的控制面板看到TCC控制端口的IP是10.10.10.2,在浏览器中访问http://10.10.10.2可以登陆CTC。成功登陆后发现这台15454的CTC版本是7.00,比上次5.0的版本高一些。但是,在CTC中选择open IOS connection并不成功,查阅15454 troubleshooting资料发现这是由于ML1000缺少初始化配置文件造成的。

第三步:配置ML1000卡

15454 Ethercard Guide第3章"Start Configuration File"中提到,在ML1000缺少初始化配置文件时,无法从CTC登陆。此时需要通过Serial Console Port或者选择从CTC载入IOS Startup配置文件。由于手头没有Startup配置文件的样本,因此选择第一种方式。找到一个console线,在服务器上运行gtkterm,根据该节"Configuring the Management Port"的步骤配置好一个ML1000卡。将该配置文件通过CTC下载本机,再使用第二种配置方式将另一个ML1000卡配置好了。

第四步:系统时钟的调整

检查CTC当前的警告信息,发现(LOS)BITS-{1,2}, (SYNCPRI)SYNC-NE的警告信息。查阅troubleshooting手册,发现这些警告是由于给15454配置了不正确的外部时钟源造成的。15454总的来说是一台SDH设备,因此会使用外部使用来进行精确的时间同步。然而在我们的实验中并没有接入外部时钟源,因此需要内部时钟源。参考procedure guide中步骤DLP-D70为15454配置内部时钟源,成功消除这些警告。

最后再看一下警告面板,只有一个PWR-B失效的警告,这是由于我们没有使用备份电源造成的。OK. 至此一台15454裸机成功配置成功。下面我们将在这台机器上开展uclp2.0的实验,zk将为你带来。

Saturday, October 07, 2006

CPU的一些常识

MIPS: Millon Instructions per second, 每秒钟指令执行速度。

时钟频率:

早期的电脑,大约每个指令需要15个时钟周期,而现在只需要1~2个时钟周期。

这是因为,现在CPU使用pipeline的技术。虽然每条指令仍需要多个时钟周期来完成,

“In a pipelined architecture, instruction execution overlaps. So even though it might take five clock cycles to execute each instruction, there can be five instructions in various stages of execution simultaneously. That way it looks like one instruction completes every clock cycle.”

64-bit CPU的好处:

1. 内存地址空间扩大,32位CPU内存大小限制2GB

2. 64-bit微机能够提供更快的I/O速度

对于普通用户,64微机带来的好处并不多。

参考:

http://computer.howstuffworks.com/microprocessor.htm

时钟频率:

早期的电脑,大约每个指令需要15个时钟周期,而现在只需要1~2个时钟周期。

这是因为,现在CPU使用pipeline的技术。虽然每条指令仍需要多个时钟周期来完成,

“In a pipelined architecture, instruction execution overlaps. So even though it might take five clock cycles to execute each instruction, there can be five instructions in various stages of execution simultaneously. That way it looks like one instruction completes every clock cycle.”

64-bit CPU的好处:

1. 内存地址空间扩大,32位CPU内存大小限制2GB

2. 64-bit微机能够提供更快的I/O速度

对于普通用户,64微机带来的好处并不多。

参考:

http://computer.howstuffworks.com/microprocessor.htm

Subscribe to:

Posts (Atom)